Enhancing data reliability and performance: Exploring On-die termination (ODT) in DDR5 memory

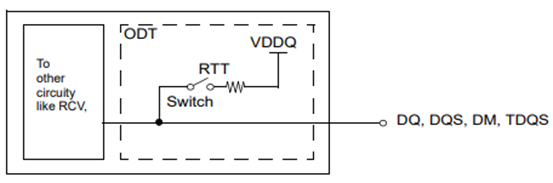

Signal integrity is more important as data is delivered at faster speeds in DDR5 memory. When there is an imbalance between the characteristic impedance of the transmission line and the impedance of the connected devices, signal reflections may happen. DDR5 (Double Data Rate 5) memory modules and other high-speed digital systems use the on-die termination (ODT) technology to lessen signal reflections and enhance signal integrity.

By placing a termination resistor that matches the transmission line’s impedance right on the memory chip, on-die termination minimizes the possibility of signal reflections. Therefore, ODT is a crucial component for high-speed DDR5 memory systems since it aids in enhancing signal quality, decreasing signal ringing, and eventually allowing for higher data transfer speeds with less signal deterioration.

[Source: DDR5 Standard [JEDEC JESD79-5B_v1.20] Page 346 of 502]

P.S. You can refer to DDR5 Standard [JEDEC JESD79-5B_v1.20]: https://www.jedec.org/sites/default/files/docs/JESD79-5B_v1-2.pdf for further studies.

With on-die termination (ODT), the termination resistor for transmission line impedance matching is housed inside a semiconductor chip as opposed to a printed circuit board (PCB). This termination resistor can be dynamically enabled or disabled depending on the settings of the memory controller and the particular needs of the memory bus.

Types of On-Die Termination (ODT) in DDR5

There are two primary ODT implementation types in DDR5 memory:

ODT in parallel (PODT)

The conventional ODT technique used in earlier DDR memory generations is called Parallel On-Die Termination. The data lines on the memory chip are connected in parallel with a fixed termination resistor in PODT. Regardless of whether the ODT is activated or disabled, this resistor offers a constant impedance to the data lines. On a memory module, the termination value is commonly selected to match the characteristic impedance of the transmission lines.

Dynamic On-Die Termination (DODT)

It is a more sophisticated ODT technology that was introduced with DDR5 memory. When using DODT, the termination impedance can be changed dynamically, in contrast to PODT. According to the settings of the memory controller and the precise data transfer requirements at any given time, the termination resistor can be changed or turned on or off. With the aid of this dynamic management, signal integrity can be improved for a range of data rates and load situations.

PODT v. DODT

Parallel ODT:

- The termination impedance in parallel ODT is constant and does not fluctuate.

- In order to change between high and low termination impedances, a mode register set instruction is necessary.

- The termination resistor is positioned on the motherboard in this example of the termination method.

Dynamic ODT:

- The DRAM may flip between high and low termination impedance thanks to dynamic ODT without requiring a mode register set instruction.

- It gives systems more freedom to choose the best termination values under various loading scenarios.

- Without executing a mode register set instruction, it enables the DRAM to alternate between high and low termination impedance.

- It simplifies and lowers the cost of the system design by reducing the amount of complicated wire and resistor parts on the motherboard.

In conclusion, the primary distinction between parallel ODT and dynamic ODT is that the former has a fixed termination impedance while the latter enables dynamic impedance switching without the requirement of a mode register set instruction. Increased flexibility and optimization for various loading circumstances are provided by dynamic ODT.

Key features of ODT in DDR5

Certainly! On-Die-Termination (ODT), which plays a critical part in guaranteeing dependable and effective high-speed data transmission, is particularly significant in DDR5 memory. ODT addresses several significant issues that develop as data transmission rates climb in contemporary memory systems. The following are the primary implications of ODT in DDR5:

Signal Reflection Reduction

Due to the nature of high-speed digital transmissions, signal reflections and impedance mismatches occur when data signals are carried across the memory bus. These reflections may deteriorate the quality of the delivered data and distort the signal. To lessen signal reflections and minimize data errors, ODT offers termination resistors that are directly attached to the memory chips and match the characteristic impedance of the transmission lines.

Data Reliability

Due to DDR5’s faster data transfer speeds, there is also a greater chance of data mistakes and corruption. Data distortions and signal ringing are reduced by proper termination utilizing ODT, resulting in more dependable data transfer and a lower probability of memory-related mistakes. ODT improves memory performance by allowing memory modules to run at their full specified speeds by reducing signal reflections and distortions.

Noise reduction

ODT aids in the memory system’s ability to filter out noise and electromagnetic interference (EMI). For signal quality to be maintained and to prevent data corruption or system instability, noise reduction is essential.

Power Efficiency

The Dynamic On-Die Termination (DODT) feature of DDR5 memory enables dynamic management of the termination impedance. DODT optimizes power usage by changing the termination parameters in accordance with the demands of the data transfer. The amount of unnecessary power dissipation is reduced, making the memory system more power-efficient.

Flexibility

DODT provides more flexibility in memory operations because it is a dynamic implementation of ODT. Memory controllers offer superior adaptability to changing circumstances by adjusting termination settings for various memory configurations, data rates, and system loads.

Intellectual property trends for ODT

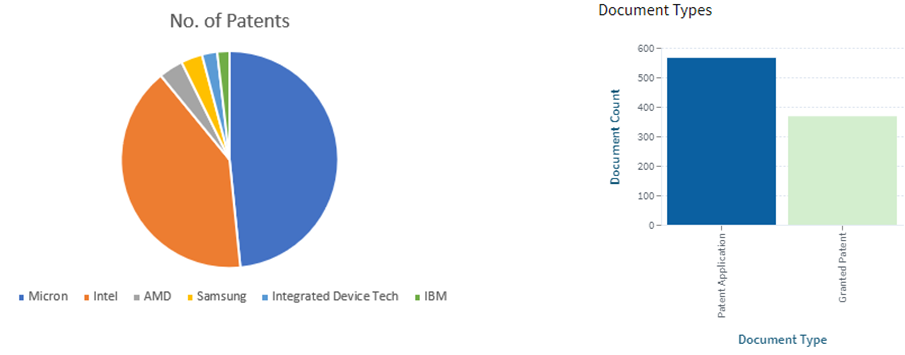

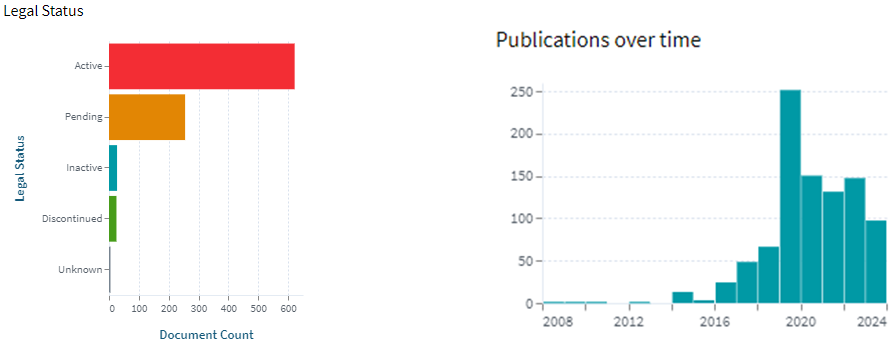

ODT in DDR5 is witnessing rapid growth in patent filing trends across the globe. Over the past few years, the number of patent applications almost getting doubled every two years.

MICRON is a dominant player in the market with ~426 patents. So far, it has 2 times more patents than Intel. AMD is the third-largest patent holder in the domain.

Other key players who have filed for patents in DDR5 technology with ODT are SK Hynix, NVDIA, Samsung, IBM, Qualcomm and IBM.

[Source: https://www.lens.org/lens/search/patent/list?q=on-die%20termination%20on%20DDR5%20memory]

Following are the trends of publication and their legal status over time:

[Source: https://www.lens.org/lens/search/patent/list?q=on-die%20termination%20on%20DDR5%20memory]

These Top 10 companies own around 54% of total patents related to HBM. The below diagram shows these companies have built strong IPMoats in US jurisdiction, followed by China, European, Korea, and Germany jurisdiction.

[Source: https://www.lens.org/lens/search/patent/list?q=on-die%20termination%20on%20DDR5%20memory]

Conclusion

ODT is becoming more and more important as memory technologies develop. Strong signal integrity and effective data transmission become more crucial with each new memory generation and higher data rates. The use of ODT in DDR5 helps memory systems be prepared for future increases in performance and data transfer speeds. In conclusion, ODT helps to provide a stable and dependable memory system that can support the needs of contemporary computer applications by reducing signal reflections and noise.